ソフトウェアによるデバウンスが適切でない場合のスイッチおよびリレーへのハードウェアデバウンスの実装方法

DigiKeyの北米担当編集者の提供

2021-02-09

電気電子工学の文脈では、スイッチは、電気回路を「メイク(make)」または「ブレーク(brake)」することができるコンポーネントであり、それによって電流を遮断したり、ある導体から別の導体に電流を迂回させたりします。エンジニアなら誰でも知っているように、スイッチには、トグルスイッチ、ロッカスイッチ、押ボタンスイッチ、マイクロスイッチ、リミットスイッチ、磁気スイッチ、リードスイッチ、リレーなど、様々なタイプのスイッチがあります。全てに共通しているのは、バウンスする(跳ね返る)ということです。スイッチとはそういうものです。

通常、このバウンスは、回路にほとんど影響を与えませんが、デジタル回路が複数のバウンスを検出して反応するのに十分な速さを持っている場合、深刻な結果を招くことがあります。エンジニアの仕事は、このバウンスの影響を回避したり、軽減したりすること、つまりスイッチを「デバウンス」させることです。この業界では長い間、ハードウェアによるデバウンスを実践してきましたが、最近ではソフトウェアによるデバウンスに移行してきています。しかし、ハードウェアデバウンスのほうが良い場合もあります。

この記事では、バウンスについて説明し、デバウンスに対するソフトウェア的なアプローチとハードウェア的なアプローチについて解説します。その上で、実装方法を示す前に、ハードウェアデバウンスの方が良いオプションである実例を示します。NKK Switches、ON Semiconductor、Texas Instruments、Maxim Integrated、LogiSwitchの事例をもとに、スイッチングデバイスやハードウェアデバウンスのコンポーネント例を紹介します。

スイッチバウンスとは?

スイッチやリレーが反転したり、切り替えられたりするとき、デバイスの状態が変化するたびに人間が瞬間的な単一の反応として認識している事象は、実際には100回以上の「メイク」または「ブレーク」動作を伴っている場合があり、接触が最終的に所定の位置に落ち着くまでに数千分の1秒の間持続します。

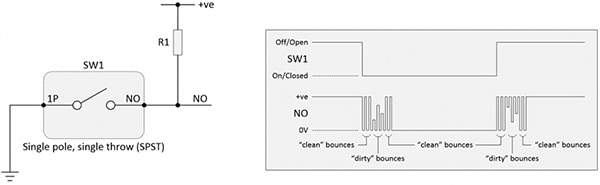

たとえば、NKKのM2011SS1W01のような単極単投(SPST)ノーマリーオープン(NO)のパネル実装トグルスイッチを考えてみます。このスイッチの一方の側(入力側とします)がグランド(0V)に接続され、もう一方の側(出力側とします)がプルアップ抵抗(R1)を介して5V電源(+veとして例示)に接続されていると仮定します(図1)。

図1:SPST-NOトグルスイッチの場合、スイッチの作動時と非作動時の両方でバウンスが発生することがあります。(画像提供:Max Maxfield氏)

図1:SPST-NOトグルスイッチの場合、スイッチの作動時と非作動時の両方でバウンスが発生することがあります。(画像提供:Max Maxfield氏)

スイッチがアクティブ(閉)と非アクティブ(開)の両方の状態で、スイッチバウンスが発生する可能性があることに注意してください。バウンスが電源レール間で遷移することがありますが、ここではロジック0と1の状態と見なされます。この場合、これらは「きれいな」バウンスです。これに対して信号が中間電圧にしか達しない場合、これらは「ダーティ」バウンスと呼ばれます。

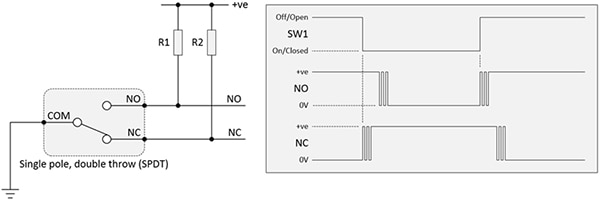

NKKのM2012SS1W01-BCのような単極双投(SPDT)パネル実装トグルスイッチの場合、ノーマリーオープン(NO)とノーマリークローズ(NC)の両方の端子でバウンスが発生することがあります(図2)。下の場合は、単純化のために「クリーンな」バウンスのみを示しています。

図2:SPDTトグルスイッチの場合、スイッチの作動時と非作動時に、NO端子とNC端子の両方でバウンスが発生することがあります。(画像提供:Max Maxfield氏)

図2:SPDTトグルスイッチの場合、スイッチの作動時と非作動時に、NO端子とNC端子の両方でバウンスが発生することがあります。(画像提供:Max Maxfield氏)

多くの場合、このような信号のバウンス持続時間は、効力がないようなものです。問題は、スイッチが電子機器の一部に接続されていて、複数のバウンスを検出して応答するのに十分な速さを持っている場合に発生します。必要とされるのは、スイッチからの信号が電子機器によって処理される前にデバウンスさせる方法です。

ソフトウェアとハードウェアのデバウンス

1960年代から1970年代にかけて、スイッチのデバウンスは、SPSTスイッチで使用されていた単純な抵抗/コンデンサ(RC)遅延回路から、より洗練されたセット/リセット(SR)ラッチ機能まで、様々なハードウェア技術を使用して実装されていました。

最近では、多くのシステムにマイクロプロセッサユニット(MPU)またはマイクロコントローラユニット(MCU)が搭載されているため、ソフトウェア技術を使用して任意のスイッチからの信号をデバウンスすることが一般的になっています。しかし、ソフトウェアのデバウンスは必ずしも最良のアプローチとは言えません。デバウンスルーチンを実装するためのコードスペースやクロックサイクルが限られている、小型で低性能、メモリに制約のあるプロセッサを使用するアプリケーションもあります。このような場合には、ハードウェアの実装がより良いソリューションになるかもしれません。

また、多くのソフトウェア開発者は、スイッチの物理特性に精通していません。たとえば、作動時に変化するだけでなく、スイッチの跳ね返り特性が温度や湿度などの環境条件の影響を受ける可能性があるのを知らないことが多いのです。

ソフトウェア開発者がスイッチの専門知識を持っていないという問題は、スイッチのバウンスに関する文献がしばしば矛盾していたり、混乱を招いたりする事実によってさらに悪化します。たとえば一般的には、スイッチのアクティブ化または非アクティブ化後、スイッチのバウンスは1ミリ秒(ms)で停止すると思われています。しかし、有名な組み込みシステムの専門家であるジャック・ガンスレ氏は、様々なタイプのスイッチを用いて、各スイッチを300回作動させ、接点の開閉の際のバウンスの最小値と最大値を記録するという実験テストを行いました。その時の平均バウンス時間は1.6ms、最大バウンス時間は6.2msと報告されています。産業用および軍事用の「ベストプラクティス」の中には、最初の作動から20ms待ってから、スイッチのバウンスが止まった見なすことを推奨するものもあれば、何らかのアクションを開始する前に最後に検出されたバウンスから20ms待つことを推奨するものもあります。

さらに、非プロセッサベースの単純なシステムでも、スイッチのデバウンスを必要とするものが多数あります。このようなシステムの例としては、リレーからのパルスをカウントする7セグメントディスプレイを駆動するバイナリカウンタ、ドアやゲートのモータ制御として使用される555ワンショットタイマへのトリガ入力、あるいはキー入力を使用するレジスタベースの有限状態機械(FSM)などがあります。また、スイッチのバウンスが問題となるようなスイッチ入力(アップ、ダウン、場合によってはストア)を使用して、値を変更した電子トリムポテンショメータ(ポット)もあります。

このような例はすべて、ハードウェアのデバウンスの実行方法に関する知識が、どのような設計者や開発者にも役立つことを明らかにしています。

RCネットワークを使用したSPSTスイッチのハードウェアデバウンス

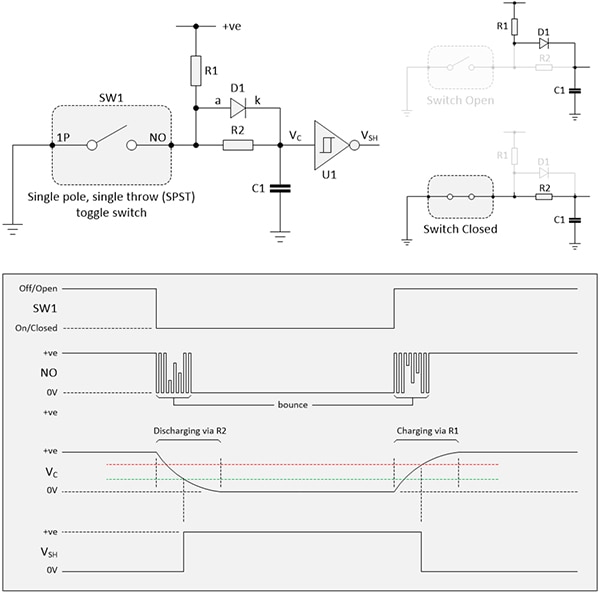

最もシンプルなハードウェアベースのスイッチデバウンスソリューションの1つは、SPSTスイッチと連動した抵抗器/コンデンサ(RC)ネットワークの使用です。このような回路には様々なバリエーションがあります。より汎用性の高い実装の1つは、2つの抵抗と1つのダイオードです(図3)。

図3:RCネットワークを使用してSPSTスイッチ(上)をデバウンスする場合、ダイオード(D1)を追加すると、コンデンサ(C1)が抵抗R1を介して充電され、抵抗R2を介して放電されます。(画像提供:Max Maxfield氏)

図3:RCネットワークを使用してSPSTスイッチ(上)をデバウンスする場合、ダイオード(D1)を追加すると、コンデンサ(C1)が抵抗R1を介して充電され、抵抗R2を介して放電されます。(画像提供:Max Maxfield氏)

スイッチがアクティブ(閉)になると、コンデンサC1は抵抗R2を介して放電されます。この回路からダイオードD1が省略された場合、スイッチが非アクティブ化(開)されたとき、C1は抵抗(R1+R2)を介して充電されることになります。しかし、D1が存在することは、C1がR1を介してのみ充電されることを意味します。

場合によっては、スイッチの作動のみが重要になる(つまり、アクションを発生させるトリガとなる)ことがあり、その場合、D1は省略できます。ただし、スイッチの作動時と非作動時の両方でアクションを発生させたい場合や、遅延を最小限に抑えることを考慮する場合は、D1を追加することを推奨します。

コンデンサ電圧VCによって示される指数関数的な充放電曲線を観察してください。この信号をダウンストリームのデジタルロジック機能の入力に送るのはお勧めできません。「正常な」ロジック0とロジック1の値の間の未定義の領域でウロウロする信号を見るのはありがたくありません。その代わりに、この信号はシュミットトリガ入力を持つバッファの入力にフィードされます。さらに、Texas InstrumentsのCD74HC14M96の1チャンネルなどのように、通常は反転バッファが使用されます。これは、反転機能が非反転機能よりも高速に切り替わるためです。

SRラッチ付きSPDTスイッチのデバウンス

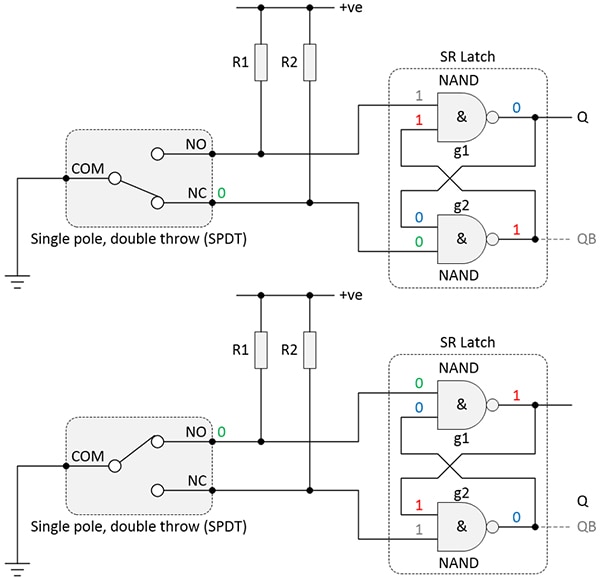

SPDTスイッチの場合、一般的なハードウェアデバウンスソリューションはSRラッチを使用することです。IBMのような企業が1960年代にメインフレームコンピュータのスイッチパネルにこの手法を使用して以来、このアプローチはシンプルなハードウェアデバウンスソリューションの最高傑作とみなされてきました。このようなラッチは、たとえば、Texas InstrumentsのSN74HC00DRクワッド2入力NAND IC(図4)の2つのチャンネルを採用することによって、2つの連続した2入力NANDゲートを使用して形成することができます。

図4:NANDベースのSRラッチを使用してSPDTスイッチをデバウンスすることは、非常に効果的なハードウェアデバウンスソリューションです。(画像提供:Max Maxfield氏)

図4:NANDベースのSRラッチを使用してSPDTスイッチをデバウンスすることは、非常に効果的なハードウェアデバウンスソリューションです。(画像提供:Max Maxfield氏)

スイッチのNC端子をグランドに接続すると、図4の上半分に示すように、これによりゲートg2の出力はロジック1に強制されます。次に、ゲートg1への入力にある2つのロジック1は、その出力をロジック0に強制的に出力します。これに対して、図4の下半分に示すように、スイッチのNO端子がグランドに接続されている場合には、これによりゲートg1の出力はロジック1に強制されます。次に、ゲートg2への入力にある2つのロジック1は、その出力をロジック0に強制します。

この回路が非常にうまく機能する理由は、両方の入力が非アクティブなロジック1の状態にあるとき、SRラッチが以前の値を記憶しているからです。図2に示すように、SPDTスイッチがトグルされると、その時点でグランドに接続されている端子のどちらかが先にバウンスすることに注意してください。これらのバウンスは元の値(ロジック0)と新しい値(ロジック1)の間にあるので、SRラッチの現在の状態には影響しません。この端子がバウンスを停止して初めて、相方の端子がバウンスし始め、その時点でSRラッチの状態が変化します。

専用デバイスによるSPSTスイッチのデバウンス

従来のソリューションの問題点の1つは、一般にSPDTよりもコストが低いため、多くの設計者がSPSTスイッチの使用を好むことです。市場には、ON SemiconductorのMC14490DWGやMaxim Integrated.のMAX6818EAP+Tなど、よく知られた専用のSPSTデバウンスデバイスが多数出回っています。

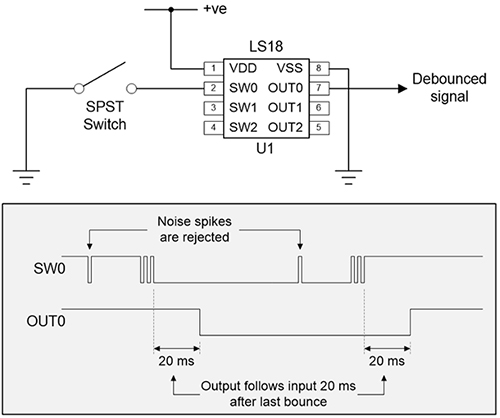

別のメーカーであるLogiSwitchは、スルーホールと面実装デバイス(SMD)の両方のパッケージで、3チャンネル、6チャンネル、および9チャンネルのデバウンスソリューションのスイートを提供しています。たとえば、LogiSwitchのLS18-Sデバイスを使った回路を考えてみましょう(図5)。

図5:専用の3チャンネルLS18-Sチップを使用してSPDTスイッチをデバウンスします(6チャンネルや9チャンネルのデバイスもあります)。(画像提供:Max Maxfield氏)

図5:専用の3チャンネルLS18-Sチップを使用してSPDTスイッチをデバウンスします(6チャンネルや9チャンネルのデバイスもあります)。(画像提供:Max Maxfield氏)

他のLogiSwitchファミリと同様に、LS18-Sは2.5~5.5Vの動作電圧範囲をサポートしています(電源電圧の値はデバイスの応答時間に影響しません)。また、一部の他の専用ICソリューションとは異なり、LogiSwitchのデバウンスデバイスは、外部クロック、RCタイミングネットワーク、入出力のプルアップ抵抗などの追加コンポーネントを必要としません。

LS18-Sは、LogiSwitch独自の適応型ノーバウンス技術を採用しており、高いレベルのノイズ耐性を実現しています。持続時間が20ms未満のノイズスパイクは、サイクルの開始または終了を禁止され、出力は、バウンスの持続時間に関係なく、アクティブ化とリリースの両方で、最後のスイッチバウンスから出力が20msの間遅延されます。

まとめ

スイッチには、トグルスイッチ、ロッカスイッチ、押ボタンスイッチなど様々な種類がありますが、どれも跳ね返り(バウンス)を起こすことがあります。もし、スイッチのバウンスが放置されていると、マイクロプロセッサや他の電子回路は、1つのスイッチの作動が複数のイベントで構成されていると見なしてしまいます。

スイッチからのバウンス信号は、マイクロコントローラで実行されるソフトウェアを使用してデバウンスされることがよくあります。これは低コストのソリューションですが、先に述べたように、性能やメモリ制限のあるマイクロコントローラをベースにしたシステム、スイッチ関連の問題についての専門知識を持たないソフトウェア開発者、マイクロコントローラなしで実装されたシステムなど、すべてのケースで最適な選択肢とは言えないでしょう。

それに代わって、RCネットワークからSRラッチ、専用集積回路に至るまで、様々なアプローチを用いてデバウンスをハードウェアで実行することができます。

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、DigiKeyの意見、信念および視点またはDigiKeyの公式な方針を必ずしも反映するものではありません。