使い慣れたツールでFPGAにエッジAIをデプロイする方法

DigiKeyの北米担当編集者の提供

2026-02-17

ネットワークエッジにおける人工知能(AI)(エッジAI)は、単なる推論のみを指すことはほとんどありません。実際の導入現場では、高速入出力(I/O)、信号調節、リアルタイム制御ループが同時に実行されるケースが一般的です。こうした多機能なワークロードは、設計者が主流のAIハードウェアでは達成が困難と感じる、緊密な連携と高い決定性レベルが求められます。

この問題をさらに複雑にする要因が2つあります。まず、AIモデルは驚異的な速度で進化しており、設計者はアルゴリズムの更新を迅速にサポートするプラットフォームの採用を迫られています。同時に、多くのエッジシステムは10年以上にわたり現場で使用され続けるため、長期的な適応性を確保することが困難です。次に、学習済みモデルから実稼働システムへの移行経路は依然として断片化されています。データサイエンティストはPyTorchやTensorFlowで作業する一方、組み込みチームは全く別のツールチェーンを使用するため、引継ぎ時の摩擦が生じ、実用化までの時間が遅くなります。

これらの課題に対処するには、エッジ導入に典型的な制約された電力枠内で、高スループットのAI処理と決定論的動作、柔軟なI/O、長期的な適応性を兼ね備えたプラットフォームが必要です。

本記事では、設計者が新たなエッジAIアーキテクチャの探求を求められるアプリケーションと関連要件を明らかにします。続いて、AlteraのエッジAI対応フィールドプログラマブルゲートアレイ(FPGA)デバイスとソフトウェアツールを紹介し、幅広い性能、消費電力のバランスにおいてこれらのアプリケーションの要件を満たす活用方法を示します。

エッジAIの進化にはアーキテクチャの革新が求められる

エッジシステムは、異常検出のための従来型機械学習(ML)、知覚処理のための畳み込みニューラルネットワーク(CNN)、大規模言語モデル(LLM)のトランスフォーマなど、多様なAI技術がますます採用されています。これらの計算集約型アルゴリズムは、信号処理、ネットワーク、リアルタイム制御といった要求の厳しい非AI機能と共存することが多々あります。

自律システムはその代表例です。自律システムは、複数のセンサモダリティ(例:動画、音声、レーダ、LiDAR、モーション/位置フィードバック)からのデータを取り込み、それらのストリームを高スループットで前処理し、高度なAIで結果を分析し、その後高精度の制御ループを管理する必要があり、これらすべてを信頼性の高い決定性をもって行うことが求められます。

産業用オートメーション、医療用画像処理、防衛、通信アプリケーションなど、各くの分野で同様の事例が見られます。共通する課題は、こうした融合するワークロードを従来のアーキテクチャで対応することが困難である点です。

エッジAIにFPGAが特に適している理由

これに対し、これらの要件はFPGAの能力に非常に適合しています。FPGAの中核は、設計時にタイミング特性を組み込み、実行時に変動することなく真の並列処理で演算を実行する構成可能なロジックを提供します。このアーキテクチャにより、エッジAIに不可欠な低レイテンシの決定論的動作が可能となります。柔軟なロジックは、強力なI/Oも活用します。FPGAは一般的に豊富な高速I/Oを備えており、多様なセンサやアクチュエータと接続可能で、AI処理との緊密な連携を実現します。

FPGAは分散型内部メモリも内蔵しており、データを処理するロジックの近くに保持します。これにより、プロセッサベースのアーキテクチャで一般的な制約である、複数の処理ステージが共有メモリバスへのアクセスを統合する際に生じるボトルネックが軽減されます。

多くのFPGAは、専用のデジタル信号処理(DSP)ハードウェアも内蔵しています。これらのハード化された回路は、汎用ファブリックよりも高い性能と優れた電力効率を、信号処理ワークロードに対して提供します。一部のFPGAには、Linuxを含む標準的なソフトウェアスタックを実行できるハードワイヤードプロセッサシステムも統合されており、ネットワーク、デバイス管理、ユーザーインターフェースなどのタスクに対して、従来のソフトウェア開発を可能にします。

要するに、I/Oチップ、AIアクセラレータ、DSP、制御プレーン用プロセッサを必要とする可能性のある機能を統合することができます。その結果、必要な部品点数(BOM)の削減、基板面積の縮小、消費電力の低減が実現され、エッジAIアプリケーションが要求する低レイテンシと決定性を維持できます。

AI Tensorブロックの追加が新たな可能性を引き出す仕組み

従来のFPGA DSPハードウェアはすでに多くのエッジのワークロードに適していますが、AI推論は高密度ながら低精度の乗累算演算が支配的となる傾向があります。この課題に対処するため、AlteraのAgilex 3およびAgilex 5デバイスは、AI Tensorブロックを備えた拡張DSPを搭載しています。これはAI演算グラフに繰り返し出現する行列間乗算およびベクトル行列乗算に特化したハードウェアです。

このアプローチの中核にあるのは、スカラー積および加算器/アキュムレータエンジンです(図1)。テンソルモードでは、ハードワイヤードドットエンジン(専用のドット積演算回路)は、8ビット入力とプリロードされた8ビット重みを使用して10要素のドット積を実行します。ダイナミックレンジを拡張するために、データパスはブロック浮動小数点スタイルのスケーリングに共有の「共通指数」を使用することも可能です。これにより、AI推論が高ダイナミックレンジと低精度が同時に求められる典型的なシナリオに対応します。

図1:AI Tensorブロックは10要素のドット積を実行できます。(画像提供:Altera)

図1:AI Tensorブロックは10要素のドット積を実行できます。(画像提供:Altera)

ドット積の結果は32ビット(固定小数点または単精度浮動小数点)であり、隣接ブロック間でより大規模なドット積を計算するために、追加の加算器/アキュムレータ段にカスケード接続することができます。各AI Tensorブロックには2つのドット積列が含まれており、多様な動作モードを実現します。

典型的な使用例では、強化された数学ハードウェアの一部が従来のDSPの役割で使用されます。たとえば、レーダデータに対する高速フーリエ変換(FFT)の実行などが挙げられます。その他では、AI Tensorブロックとして使用され、たとえば、物体検出を行うCNNなどに活用されます。この柔軟性は、AI処理と他の計算集約型機能を同時に処理しなければならないエッジシステムにとって極めて重要です。

さまざまなAIワークロードに対応する幅広いFPGAオプション

Agilexファミリは、性能の拡張性においても非常に高い柔軟性を提供します。製品ラインアップは、わずか12mm × 12mmの効率重視デバイスから、最大152.6ピークテラ演算/秒(TOPS)を実現する高性能バリエーションまで幅広く、I/Oおよびメモリインターフェース機能においても同様の拡張性を備えています。

高性能デバイスの例として、Agilex 5 A5ED065BB32AE4SR0が挙げられます。これは32 × 32mmのパッケージで22.17TOPSを実現します。効率性を重視したデバイスの例としては、16 ×16mmパッケージで2.8TOPSを実現するAgilex 3 A3CW135BM16AE6Sが挙げられます。各製品の主な仕様を表1に示します。

|

表 1:サンプルとなるAgilex 5およびAgilex 3 FPGAの主な仕様の一部を示します。(表提供:Altera(筆者により変更))

両ファミリとも、従来のFPGAとして、あるいはArmプロセッサを統合したシステムオンチップ(SoC)としても利用できます。Agilex 3 SoCは、デュアルコア、800メガヘルツ(MHz)のArm Cortex-A55を搭載しています。Agilex 5 SoCは、デュアル1.8ギガヘルツ(GHz)Cortex-A76コアとデュアル1.5GHz Cortex-A55コアを組み合わせた非対称クラスタを特長としています。どちらの構成もLinuxをサポートしており、ネットワーク、デバイス管理、ユーザーインターフェース向けの従来のソフトウェア開発が可能です。

FPGAを用いたエッジAI導入の簡素化

AIモデルは通常、迅速な設計サイクルを特長とするソフトウェア中心のフレームワークで開発されますが、FPGAの実装には従来、ハードウェア開発スキルとより長い統合サイクルが必要でした。AlteraのFPGA AIスイート(図2)は、業界標準のAIツールと互換性のあるフローを用いることで、学習済みモデルから展開可能なFPGA推論用知的財産(IP)へのより直接的な道筋を提供します。

図2:FPGA AIスイートのワークフローは、標準的なAIフレームワークとFPGAデプロイメントへの橋渡しをします。(画像提供:Altera)

図2:FPGA AIスイートのワークフローは、標準的なAIフレームワークとFPGAデプロイメントへの橋渡しをします。(画像提供:Altera)

このワークフローをまとめると以下のようになります。

- PyTorch、TensorFlow、ONNXなどの標準的なフレームワークで推論モデルを開発します。

- OpenVINOツールキットを使用して、モデルを中間表現(IR)に変換します。このIRは、グラフファイル(.xml)と重み(.bin)で構成されます。

- IRアーティファクトをFPGA AIグラフコンパイラに渡します。これにより、モデルが利用可能なFPGAリソースにマッピングされます。このようなリソースには、外部ホストプロセッサ、内部プロセッサ、またはヘッドレス構成などが含まれます。

- Quartus Prime Pro Editionを使用して、生成された(各ネットワーク)層をコンパイルおよびデプロイし、推論エンジンランタイムスタックと、メモリ移動およびハードウェアスケジューリング用のFPGA AIアプリケーションプログラミングインターフェース(API)を通じて実行を管理します。

- コンパイルプロセスの一環として、Architecture Optimizer(アーキテクチャオプティマイザ)を使用して、パフォーマンスとリソース使用量のバランスをとります。たとえば、推論スループット目標を達成しつつ、他のFPGAロジックのための余地を確保するために使用します。

実用的な観点から、このアプローチの価値は、「FPGAへのデプロイ」をアクセラレータ設計作業ではなく、統合プロセスへと転換する点にあります。データサイエンティストは、確立されたモデル開発ワークフローを維持できる一方、FPGAおよび組み込みチームは、ビルドおよびデプロイサイクルに自然な形で適合する成果物を受け取ります。これにより、モデルや要件が進化する中で、より迅速な設計サイクルが可能になります。OpenVINOツールキット向けOpen Model Zooで利用可能な事前学習済みモデルは、開発をさらに加速させることが可能です。

使いやすい開発キットで素早く開発

FPGA上でエッジAIの探求を開始するため、設計者には複数の開発キットオプションが用意されています。より高性能なアプリケーションには、Terasic P0775Atum A5開発キット(図3)が適しています。Agilex 5 A5ED065BB32AE4SR0を中心に構築された本キットは、エッジクラスのシステムに適した幅広いインターフェースの組み合わせを提供します。主な機能としては、8ギガバイト(Gバイト)のDDR4、QSFP+および2.5ギガビット(Gビット)Ethernet(GbE)ポート、PCIe Gen 3 x 4、デュアルMIPIカメラコネクタ、HDMI出力を備えています。本キットにはQuartus Prime Pro Editionの無償ライセンスが含まれています。

図3:P0775 Atum A5開発キットは、高性能AIおよびビジョン開発へのアクセスを提供します。(画像提供:Terasic)

図3:P0775 Atum A5開発キットは、高性能AIおよびビジョン開発へのアクセスを提供します。(画像提供:Terasic)

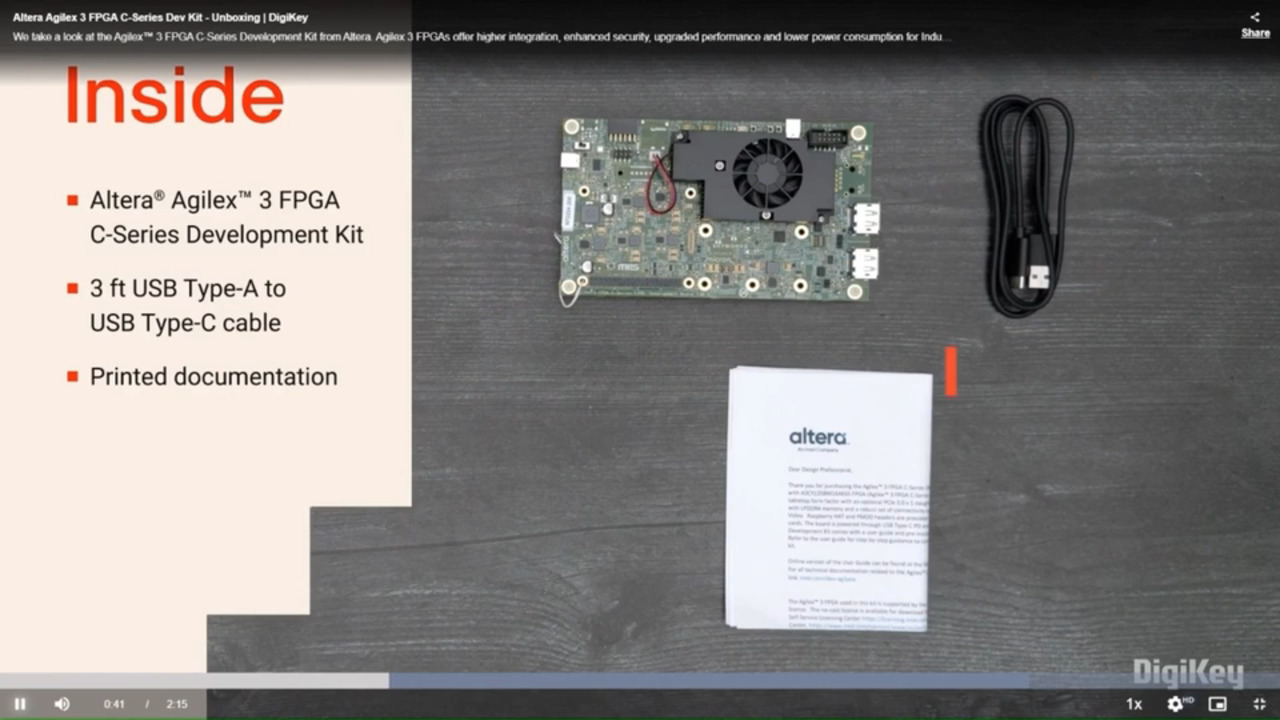

効率性を重視したアプリケーション向けに、設計者はDK-A3W135BM16AEAAgilex 3 FPGAおよびSoC Cシリーズ開発キットを利用できます(図4)。Agilex 3 A3CW135BM16AE6Sを中心に構築されたこのキットは、小型の試作とエコシステムに配慮した拡張性を重視しています。基板には4ギガバイトのLPDDR4、GbE、DisplayPort、USB 2.0に加え、Raspberry Pi HATコネクタ、Digilent Pmodインターフェースを搭載し、手軽な機能拡張を実現しています。

図4:DK-A3W135BM16AEA Agilex 3 FPGAおよびSoC Cシリーズ開発キットは、効率性を重視したエッジAI向けの小型なプラットフォームを提供します。(画像提供:Altera)

図4:DK-A3W135BM16AEA Agilex 3 FPGAおよびSoC Cシリーズ開発キットは、効率性を重視したエッジAI向けの小型なプラットフォームを提供します。(画像提供:Altera)

まとめ

エッジ環境におけるLLMやその他の新しいAIワークロードの導入は、開発者による新たなアプローチの模索を促しています。FPGAは、低レイテンシで決定論的な性能を提供するだけでなく、他の多くのシステム機能も処理できる独自のソリューションを提供します。AI対応のAgilex FPGAとFPGA AIスイートにより、開発者はこれらの機能を迅速かつ容易に活用でき、高度に適応性があり長寿命な設計のための新たなアーキテクチャの可能性が開かれます。

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、DigiKeyの意見、信念および視点またはDigiKeyの公式な方針を必ずしも反映するものではありません。