データ収集信号チェーンシミュレーションで部品選択とテストを簡素化

DigiKeyの北米担当編集者の提供

2025-11-24

データ収集システムの設計は、かつては大量のデータシートの中から適切な部品の組み合わせを探したり、寄せ集めたプロトタイプのトラブルシューティングを行ったりすることを意味していました。現在、設計者は、センサ、アナログ信号調整ブロック、A/Dコンバータ(ADC)、デジタルフィルタなどの部品のモデルを仮想信号チェーンにドラッグアンドドロップできるデジタル設計ツールを使用して、時間とフラストレーションを節約できます。ソフトウェアが仮想チェーンの出力をシミュレートするため、設計者は、選択した部品がSNR(信号対ノイズ比)、ゲイン、オフセット誤差、電力などの結果にどのように影響するかを確認できます。

Analog Devices, Inc.(ADI)のデジタル設計スイートであるPrecision Studioには、設計者がデータ収集システムを構築する前にシミュレートするのに役立つモジュール「Signal Chain Designer」が含まれています。Signal Chain Designerでは、ユーザーはセンサを選択し、モデルのパラメータを設定した後、信号チェーンの部品を表す回路ブロックをドロップします(図1)。

図1:ADIのPrecision Studio内のSignal Chain Designerでは、設計者はセンサを選択し、回路ブロックをチェーンにドラッグアンドドロップしてデータ収集部品をシミュレートできます。(画像提供:Analog Devices, Inc.)

図1:ADIのPrecision Studio内のSignal Chain Designerでは、設計者はセンサを選択し、回路ブロックをチェーンにドラッグアンドドロップしてデータ収集部品をシミュレートできます。(画像提供:Analog Devices, Inc.)

センサ信号は、信頼できるデータになるまでにいくつかのステージを通過する必要があり、各ステージは、信号を次のステージに準備する1つ以上の電子部品または集積回路(IC)で構成されています。最も一般的なステージは、アナログ信号を増幅し、アナログ信号をフィルタし、アナログ信号をデジタルに変換し、デジタル信号をフィルタします。

アナログ信号増幅ステージ

センサによって生成されるアナログ信号は、データ収集システムの最適入力と一致しないことが多々あります。アナログ信号増幅ステージでは、オペアンプ、完全差動アンプ、電圧リファレンス、および抵抗、コンデンサ、インダクタなどの受動部品を使用して、センサ信号をデータ収集システム用の効率的な形式に変換します。

Signal Chain Designerでは、アナログ増幅ステージの入力および出力タイプ、必要なゲイン、正しい電圧入力を達成するために必要なレベルシフトを指定します。その後、ADI製品を使用して指定されたパラメータを満たす回路を作成し、回路図を出力します。

たとえば、図1のセンサ(1kHzでインピーダンス1kΩ、静電容量100pF)の場合、ユーザーは2V/Vのゲインと2.5Vのレベルシフトを指定することができます(図2)。

図2:Signal Chain Designerのユーザーは、アナログ信号増幅ステージの構成、ゲイン、レベルシフト、その他のパラメータを指定します。(画像提供:Analog Devices, Inc.)

図2:Signal Chain Designerのユーザーは、アナログ信号増幅ステージの構成、ゲイン、レベルシフト、その他のパラメータを指定します。(画像提供:Analog Devices, Inc.)

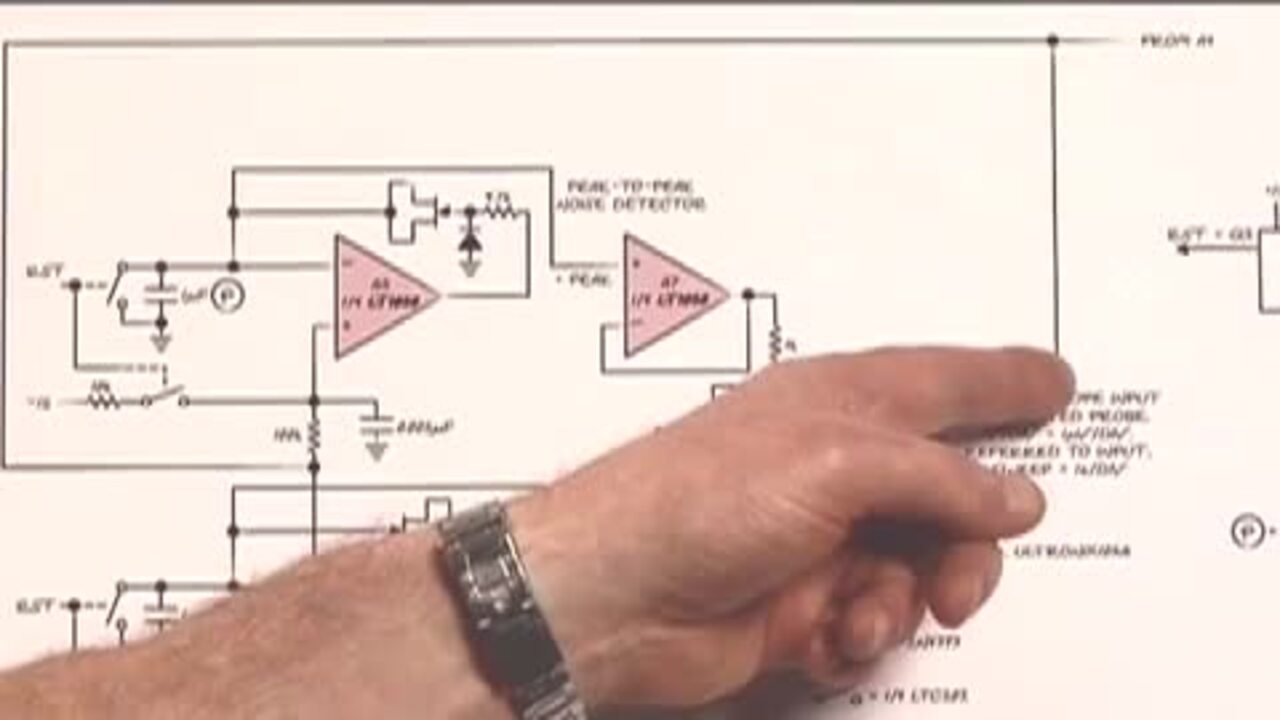

これらのパラメータに基づいて、ソフトウェアはADA4097-2オペアンプを含むアナログ信号増幅ステージ(図3、上)の回路図を作成します。ADA4097-2ファミリのオペアンプは、大信号電圧ゲインで130kHzのゲイン帯域幅積(GBP)を達成するために、1チャンネルあたりわずか32.5µAしか必要とせず、0.1Hz~10Hzの間で1,000nVのピーク-ピーク(P-P)ノイズ、6Hzで標準1/fノイズコーナーを実現します。

このソフトウェアは、ADIのLTC6655B-2.5高精度バンドギャップ電圧リファレンスとAD8510オペアンプ(図3、下)を使用したアンプステージのリファレンス回路も開発します。

図3:ユーザーの仕様に基づき、ADIの適切な電子部品を含むSignal Chain Designerのアナログ信号増幅ステージ回路図。(画像提供:Analog Devices, Inc.)

図3:ユーザーの仕様に基づき、ADIの適切な電子部品を含むSignal Chain Designerのアナログ信号増幅ステージ回路図。(画像提供:Analog Devices, Inc.)

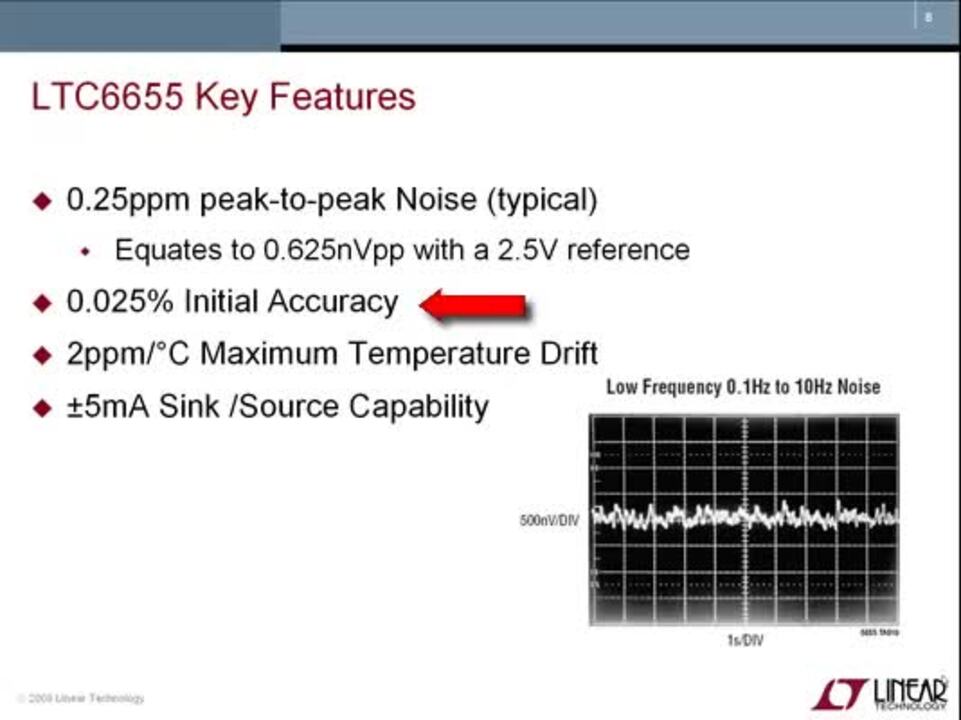

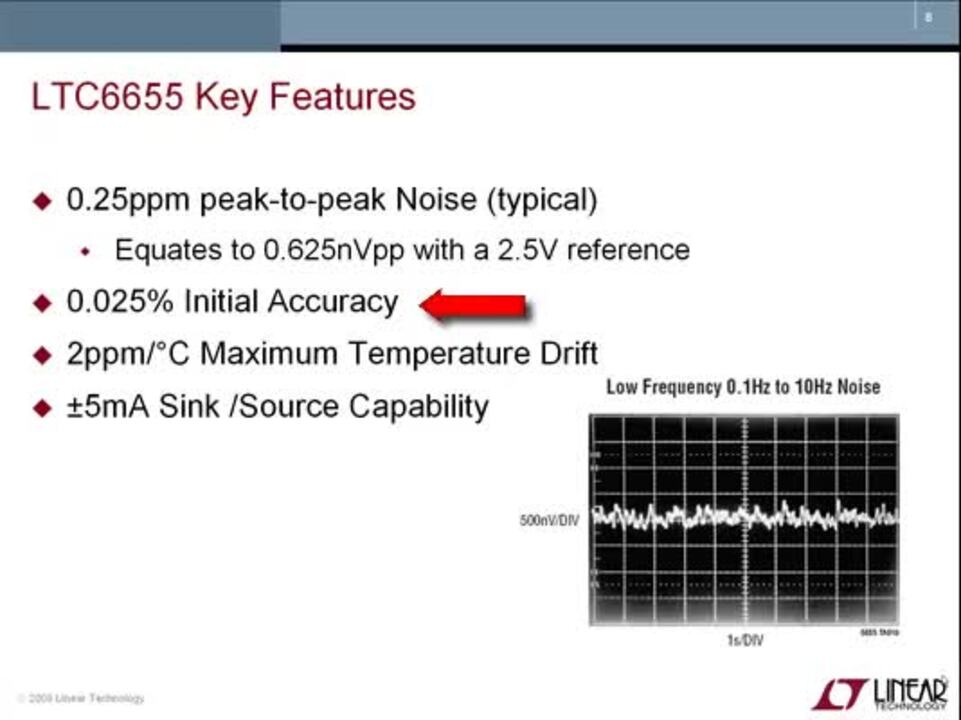

LTC6655B-2.5のノイズは0.25ppmP-P(0.1Hz~10Hz、625nVP-P)で、最大精度は±0.025%、電圧ドリフトは最大2ppm/°Cと低く、入力電圧や負荷の変動にかかわらず安定した信号電圧を出力します。 AD8510ジャンクション電界効果トランジスタ(JFET)オペアンプは、1kHzで8nV(標準)のスペクトルノイズを持ち、わずか25pAの入力バイアス電流しか必要とせず、500ns以内に0.1%の誤差範囲に落ち着きます。

Signal Chain Designerでは、このステージで信号がどのように調整されるかを指定することもできます。ユーザーは完全差動アンプ、計装アンプ、電流センスアンプを構成できます。

アナログ信号フィルタリングステージ

増幅されたアナログ信号は、次に増幅によって生じたノイズや歪みを除去するためにフィルタリングする必要があります。フィルタは、抵抗やコンデンサなどの受動部品を使って、カットオフ周波数の後に-20dB/decadeの緩やかなロールオフを持つ1次フィルタを作成できます。2次以上のフィルタは通常、よりシャープなロールオフを実現するために1つ以上のオペアンプを使用するアクティブフィルタです。

フィルタの構成によって、中心周波数f0より上の周波数を減衰させるか(ローパス)、f0より下の周波数を減衰させるか(ハイパス)、2つのカットオフ周波数の外側を減衰させるか(バンドパス)、特定の周波数帯域の外側を減衰させるか(バンドストップまたはノッチ)が決まります。Q値などの他のフィルタパラメータは、フィルタ応答をさらに微調整し、ロールオフの鋭さ、過渡挙動、通過帯域の形状を定義します。

Signal Chain Designerでは、フィルタタイプを選択し、主要なパラメータを指定することで、シンプルなフィルタのパラメータを構成できます。Signal Chain DesignerのFilter Wizardは、3次以上のフィルタを使用してシンプルなフィルタを設計し、そのフィルタをデジタル信号チェーン設計にインポートすることもできます。この例(図4)では、ユーザーはf0が10kHz、Q値が0.707のローパスフィルタを選択しています。選択されたSallen-Keyタイプのフィルタは、単一のオペアンプを使用し、高入力インピーダンスを受け入れ、安定性の良い低インピーダンス信号を出力します。

図4:ユーザーはSignal Chain Designerで、フィルタタイプ、f0、Q値、ゲインを含むアナログフィルタリングステージのパラメータを定義します。(画像提供:Analog Devices, Inc.)

図4:ユーザーはSignal Chain Designerで、フィルタタイプ、f0、Q値、ゲインを含むアナログフィルタリングステージのパラメータを定義します。(画像提供:Analog Devices, Inc.)

これらのパラメータにより、Signal Chain DesignerはADIのLT6020レールツーレールオペアンプを含む回路を出力します(図5)。LT6020の消費電流は100µA未満ですが、スルーレートは5V/µsで、入力信号の変化に素早く反応します。GBPは-40°C〜+125°Cの温度範囲で400kHzです。

図5:Signal Chain Designerが出力するアナログ信号フィルタステージの回路図では、ローパスのSallen-Key 2次フィルタとして、スルーレートが高く消費電力が低いLT6020オペアンプを指定しています。(画像提供:Analog Devices, Inc.)

図5:Signal Chain Designerが出力するアナログ信号フィルタステージの回路図では、ローパスのSallen-Key 2次フィルタとして、スルーレートが高く消費電力が低いLT6020オペアンプを指定しています。(画像提供:Analog Devices, Inc.)

アナログ/デジタル変換ステージ

センサ応答からデータへの信号経路における最終段階は、アナログ信号をデジタル形式に変換することです。一般的なADCアーキテクチャには、中程度のサンプリングレートで良好な分解能を実現する逐次比較レジスタ(SAR)と、低サンプリングスピードで高分解能を実現するデルタシグマ(ΔΣ)があります。希望するデジタル出力を得るためには、設計者は入力タイプ、システム分解能、出力データレートを把握している必要があります。

ユーザーはSignal Chain Designerでこれらのパラメータを指定し、ソフトウェアは入力の電圧リファレンスとパッシブ抵抗/容量(RC)フィルタを含むADC回路を出力します。ADCの中には、デジタルフィルタリングを内蔵したり、よりシンプルで低電力の設計向けにADCを高インピーダンス(Hi-Z)モードに設定できるものもあります。

この例(図6)では、Signal Chain Designerの出力がADIのADR4525電圧リファレンスとAD7175-2 ΔΣ ADCを指定しました。ADR4525は、0.8ppm/°C~4.0ppm/°Cの温度係数で良好な温度安定性を持ち、出力ノイズは2.048VOUT、0.1Hz~10Hzで1µVP-Pです。AD7175-2は、250,000サンプル/秒(250kSPS)のスループットと20µsのセトリング時間を持つ24ビットADCです。

図6:アナログ/デジタル変換ステージでは、Signal Chain Designerの回路図にパッシブRC入力フィルタ、電圧リファレンス、ADCモジュールが含まれます。(画像提供:Analog Devices, Inc.)

図6:アナログ/デジタル変換ステージでは、Signal Chain Designerの回路図にパッシブRC入力フィルタ、電圧リファレンス、ADCモジュールが含まれます。(画像提供:Analog Devices, Inc.)

信号チェーンのどのステージでも、ユーザーは適切な代替部品を示す製品表を閲覧できます。たとえば、設計者は、例に示したΔΣ ADCの代わりにAD4008などのSAR ADCを選択することができます。AD4008の消費電力は10kSPSで70μW~2MSPS(最大電力)で14mWの範囲となります。擬似差動動作により、Hi-Zモードでは簡素化された設計で16ビット精度を実現します。

アナログ/デジタル変換後、設計者はSignal Chain DesignerでADCの下流設計にデジタルフィルタブロックをドロップすることにより、出力を最適化できます。これらのデジタルフィルタリングブロックのオプションには、平均、1次および2次フィルタ、単純な移動平均CICフィルタなどがあります。

Signal Chain Designerを使用して仮想データ収集システムを構築した後、ユーザーはソフトウェア内から周波数応答、ノイズ、DC誤差バジェット、電力、入力範囲をシミュレートできます。よりカスタマイズされたシミュレーションのために、Signal Chain Designerは、LTspiceで編集して実行できる仮想テストベンチを作成できます。

まとめ

ADIのSignal Chain Designerなどのデジタルツールは、精密データ収集システムの構築における当て推量やフラストレーションを最小限に抑えることができます。Signal Chain Designerでは、入手しやすいさまざまなオペアンプ、電圧リファレンス、ADC、その他の部品のモデルがソフトウェア内に用意されているため、ユーザーはデータ収集システムをバーチャルに微調整することができ、ハードウェアの入手や導入へのスムーズな移行が可能になります。

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、DigiKeyの意見、信念および視点またはDigiKeyの公式な方針を必ずしも反映するものではありません。