Renesas RZ/V2シリーズ MPUによる視覚認識システム設計の加速化

DigiKeyの北米担当編集者の提供

2022-09-29

多くの製品においてエッジでの視覚認識がますます重要な機能となるにつれて、機械学習(ML)や人工知能(AI)が幅広いアプリケーション領域で活用されるようになっています。開発者が直面する問題は、ML/AI対応ビジョンが認識アルゴリズムを実行するために、電力に制約のあるアプリケーションで利用可能な計算能力よりも多くの計算能力を必要とする可能性があることです。高価な熱管理ソリューションが必要な場合は、コストも増加します。

エッジにおけるML/AIの目標は、性能と電力のバランスを取りながら、アプリケーションを開発するための堅牢なソフトウェアエコシステムを提供する最適なアーキテクチャアプローチを見つけることです。

このような状況を踏まえ、この記事では、AIハードウェアアクセラレータを内蔵したRenesas ElectronicsのRZ/V2シリーズ マイクロプロセッサユニット(MPU)によるソリューションを紹介します。この記事では、マイクロコントローラ(MCU)やハイエンドのグラフィックス処理ユニット(GPU)ではなく、MPUによって設計者の直面する諸問題をどのように解決できるかを考察します。RZ/V2シリーズを使用して視覚認識システムの設計を始める方法を解説し、そのプロセスを円滑に進めるための「ヒントとコツ」をいくつか紹介します。

RZ/V2シリーズ MPUの紹介

RZ/V2シリーズは、3コアのマイクロプロセッサを使用して、開発者のために多くの機能を解放するソリューションです。RZ/V2Lシリーズ マイクロプロセッサは、1.2GHzで動作するArm Cortex-A55プロセッサ2個と、200MHzで動作するリアルタイムマイクロコントローラコア(Arm® Cortex®-M33)1個を搭載しています。さらに、このシリーズの部品には、NEONの単一命令複数データ(SIMD)命令を備えたArm Mali-G31マルチメディアプロセッサをベースにしたGPUが搭載されています。これら3個のプロセッシングコアとマルチメディアプロセッサを組み合わせることで、視覚認識システムに取り組む開発者に包括的なソリューションを提供します。

現在、RZ/V2シリーズには、RZ/V2LシリーズとRZ/V2Mシリーズという2つのMPUクラスが存在します。RZ/V2Lは、シンプルなイメージシグナルプロセッサ(ISP)、3Dグラフィックスエンジン、および汎用性の高い周辺機器セットを備えています。一方、RZ/V2Mには、30fpsで4K解像度に対応した高性能ISPが追加されています。この記事では、R9A07G054L23GBGとR9A07G054L24GBGで構成されるRZ/V2Lファミリに焦点を当てます。2つの部品の主な違いは、R9A07G054L23GBGが15mm2の456-LFBGAパッケージで提供され、R9A07G054L24GBGは21mm2の551-LFBGAパッケージで提供されることです。

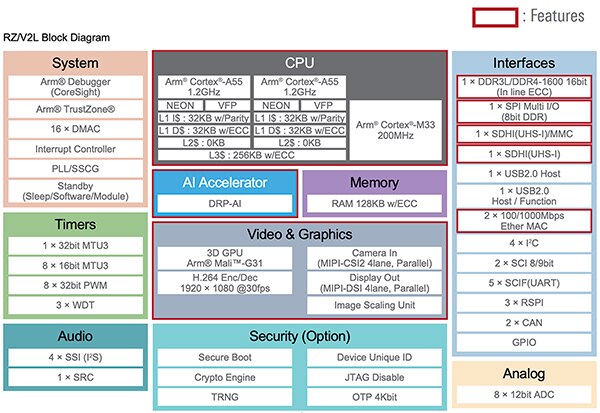

RZ/V2Lシリーズのブロック図を、図1に示します。MPUには、3個のプロセッシングコアに加え、DDR3/DDR4メモリ、SPI、USB、Ethernet、I²C、CAN、SCI、GPIO、A/Dコンバータ(ADC)など、標準的な周辺機器のインターフェースも搭載されています。さらに、セキュアブート、暗号エンジン、真乱数発生器(TRNG)などのセキュリティ機能が搭載されています。しかし、MPUシリーズが他と異なるのは、動的再構成プロセッサ(DRP)のAIアクセラレータです。

図1:RZ/V2L MPUシリーズは、さまざまな周辺機器インターフェース、セキュリティ、ビデオ処理のオプションに対応しています。視覚認識アプリケーションに不可欠な機能は、DRP-AIアクセラレータです。(画像提供:Renesas Electronics Corporation)

図1:RZ/V2L MPUシリーズは、さまざまな周辺機器インターフェース、セキュリティ、ビデオ処理のオプションに対応しています。視覚認識アプリケーションに不可欠な機能は、DRP-AIアクセラレータです。(画像提供:Renesas Electronics Corporation)

DRP-AIアクセラレータの秘密

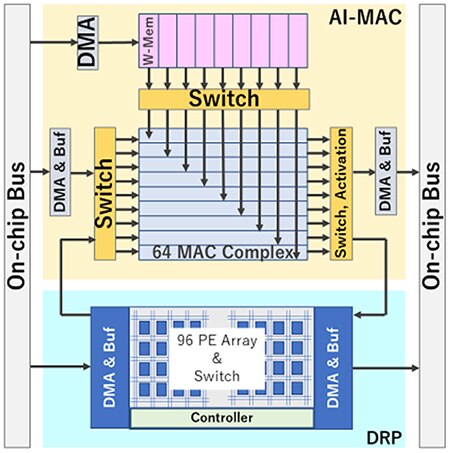

DRP-AIアクセラレータは、RZ/V2LシリーズのMPUがエネルギー消費と温度プロフィールを低く抑えつつ、視覚認識アプリケーションを迅速に実行できるようにするための秘密となっています。DRP-AIは、DRPとAI-MAC(AI-multiply-and-accumulate)という2つのコンポーネントで構成され、内部スイッチによるデータフローの最適化により、畳み込みネットワークや全結合層での演算を効率的に処理します(図2)。

DRP-AIハードウェアは、AI推論専用です。DRP-AIは、Renesasが開発した独自の動的再構成技術を使用して、高い柔軟性、高速処理、電力効率を実現しています。また、無償のソフトウェアツールであるDRP-AIトランスレータにより、ユーザーは最適化されたAIモデルを実装し、迅速に性能を最大化できます。DRP-AIトランスレータが出力する複数の実行ファイルは、外部メモリに配置できます。次に、アプリケーションはランタイム中に複数のAIモデルを動的に切り替えることができます。

DRPは、ハードウェア構成を動的に変更することで、画像の前処理やAIモデルのプーリング層など、複雑なアクティビティを迅速に処理できます。

図2:DRP-AIはDRPとAI-MACで構成され、内部スイッチによるデータフローの最適化により、畳み込みネットワークや全結合層での演算を効率的に処理できます。(画像提供:Renesas Electronics Corporation)

図2:DRP-AIはDRPとAI-MACで構成され、内部スイッチによるデータフローの最適化により、畳み込みネットワークや全結合層での演算を効率的に処理できます。(画像提供:Renesas Electronics Corporation)

DRP-AIトランスレータ

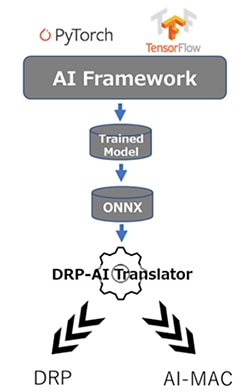

DRP-AIトランスレータツールは、AIフレームワークに依存しないトレーニング済みのONNXモデルから、DRP-AIに最適化した実行ファイルを生成します。たとえば、ONNXモデルを出力するのであれば、PyTorch、TensorFlow、または他のAIモデリングフレームワークを使用することができます。モデルのトレーニングが終わると、DRP-AIトランスレータにモデルが供給され、DRPとAI-MACの実行ファイルが生成されます(図3)。

図3:AIモデルは、ONNX互換のフレームワークを使用してトレーニングされます。次に、ONNXモデルはDRP-AIトランスレータに供給され、DRPとAI-MACの実行ファイルが生成されます。(画像提供:Renesas Electronics Corporation)

図3:AIモデルは、ONNX互換のフレームワークを使用してトレーニングされます。次に、ONNXモデルはDRP-AIトランスレータに供給され、DRPとAI-MACの実行ファイルが生成されます。(画像提供:Renesas Electronics Corporation)

DRP-AIトランスレータの主な目的は3つあります。

- AIモデルを処理するために各操作をスケジューリングします。

- 各操作の遷移時に発生するメモリアクセス時間などのオーバーヘッドを、スケジュール内で非表示にします。

- ネットワークグラフの構造を最適化します。

このトランスレータは、AIモデルの各プロセスをAI-MACとDRPに自動的に割り当てるため、ハードウェアの専門家でなくても、簡単にDRP-AIを利用できます。その代わり、開発者は付属のドライバを介して呼び出すことで、高性能なAIモデルを実行できます。加えて、DRP-AIトランスレータは、ハードウェアを変更することなく、新しく開発されたAIモデルに対応するために、継続的にアップデートすることが可能です。

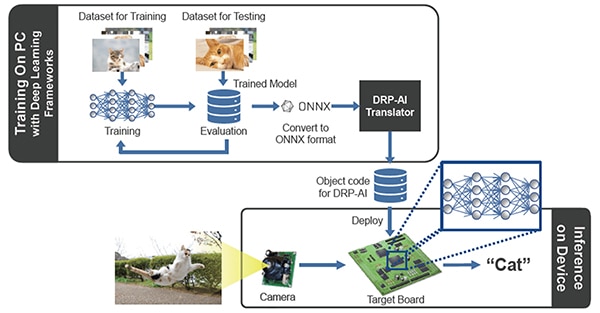

システムの使用事例とプロセス

RZ/V2L MPUを使用して視覚認識アプリケーションをトレーニングおよび展開する際の一般的なプロセスの流れを、図4に示します。従来通り、技術者はデータセットを取得し、それを使用して視覚認識モデルをトレーニングできます。猫を識別するにしても、買い物かごの中の製品や組み立てラインで故障した部品を識別するにしても、使い慣れたAIフレームワークを使用したトレーニングプロセスが発生します。トレーニングされたモデルはONNX形式に変換され、DRP-AIトランスレータに供給されます。次に、DRP-AIハードウェアで実行可能なオブジェクトコードが出力されます。カメラ、加速度計、または他のセンサからのデータをサンプリングして実行ファイルに供給し、推論を実行した結果が提供されます。

図4:RZ/V2L MPUにおける視覚認識アルゴリズムのトレーニングと実行のプロセス。(画像提供:Renesas Electronics Corporation)

図4:RZ/V2L MPUにおける視覚認識アルゴリズムのトレーニングと実行のプロセス。(画像提供:Renesas Electronics Corporation)

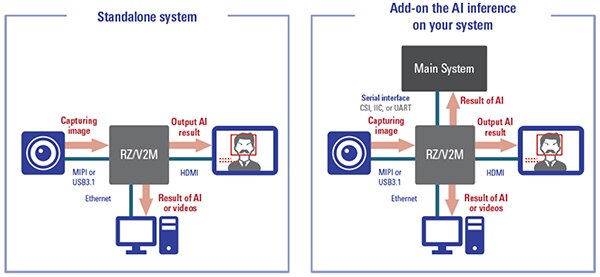

技術者がRZ/V2L MPUを設計に活用する方法はいくつかあります(図5)。まず、RZ/V2L MPUは、システム内でRZ/V2Lのみをプロセッサとするスタンドアロン設計で使用できます。3つのコアとAIアクセラレーションハードウェアを搭載しているため、追加の演算能力は必要ありません。

2つ目の使用事例は、RZ/V2Lをより大規模なシステムのAIプロセッサとして使用する場合です。この使用事例では、RZ/V2LがAI推論を実行し、結果を他のプロセッサやシステムに返します。次に、プロセッサやシステムはその結果に基づいて動作します。選択される使用事例は、コスト、システム全体のアーキテクチャ、性能、リアルタイム応答の要件など、さまざまな要因に依存します。

図5:RZ/V2L MPUの2つの使用事例は、アプリケーションにスタンドアロンで使用する場合と、より大規模なシステムでAIプロセッサとして使用する場合です。(画像提供:Renesas Electronics Corporation)

図5:RZ/V2L MPUの2つの使用事例は、アプリケーションにスタンドアロンで使用する場合と、より大規模なシステムでAIプロセッサとして使用する場合です。(画像提供:Renesas Electronics Corporation)

実世界アプリケーションの例

視覚認識技術を展開できる使用事例は、数多くあります。興味深いのは、スーパーマーケットでの事例です。今日、食料品店で会計をする際、従業員や買い物客は通常、買い物かごの中のすべての商品をスキャンします。興味深い使用事例の1つは、コンベアを横切る商品を視覚認識で検知し、自動的に課金することです。

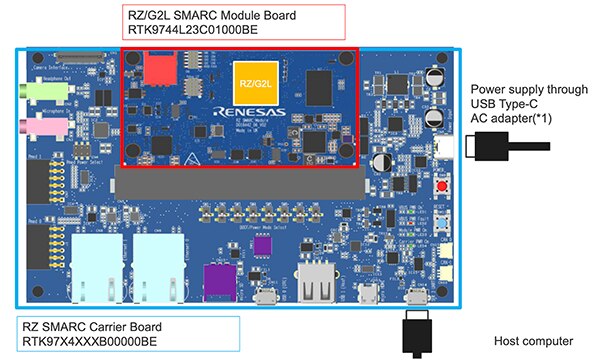

簡単なCMOSカメラとRenesasのRTK9754L23S01000BE評価ボードを使用すれば、試作を構築できます(図6)。RZ/V2L組み込み開発ボードは、システムオンモジュール(SOM)とキャリアボードを搭載しており、開発者は短期間で立ち上げることができます。また、この開発ボードはLinuxに加え、DRP-AIトランスレータなどの各種ツールにも対応します。

図6:RZ/V2L組み込み開発ボードは、SOMとキャリアボードを搭載しており、開発者は短期間で立ち上げることができます。(画像提供:Renesas Electronics Corporation)

図6:RZ/V2L組み込み開発ボードは、SOMとキャリアボードを搭載しており、開発者は短期間で立ち上げることができます。(画像提供:Renesas Electronics Corporation)

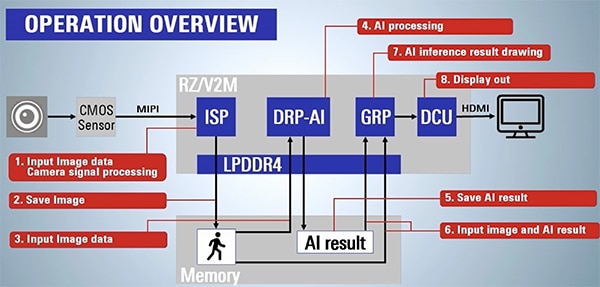

画像データを取得してAI結果を生成するために必要な操作の概要を、図7に示します。このアプリケーション例では、オンボードISPを介して、CMOSセンサでコンベアベルトの画像を撮影しています。次に、画像をメモリに保存し、DRP-AIエンジンに供給します。最後に、DRP-AIエンジンが推論を実行し、AI結果を提供します。その結果、たとえば、バナナが見つかったり、リンゴや他の果物が見つかったりします。

多くの場合、結果には0~1の信頼度が添えられます。たとえば、0.90の信頼度は、リンゴを検出したとAIが確信していることを意味します。一方、信頼度が0.52であれば、AIはそれがリンゴだと思っているが、不確かであることを意味します。AIの結果を複数のサンプルで平均化することで、正しい結果が得られる確率を高めるのが一般的です。

図7:RZ/V2L組み込み開発ボードを使用して、コンベアベルト上のさまざまな果物を認識するAI推論を実行します。この図は、画像を取得してAI結果を生成するために必要な手順を示しています。(画像提供:Renesas Electronics Corporation)

図7:RZ/V2L組み込み開発ボードを使用して、コンベアベルト上のさまざまな果物を認識するAI推論を実行します。この図は、画像を取得してAI結果を生成するために必要な手順を示しています。(画像提供:Renesas Electronics Corporation)

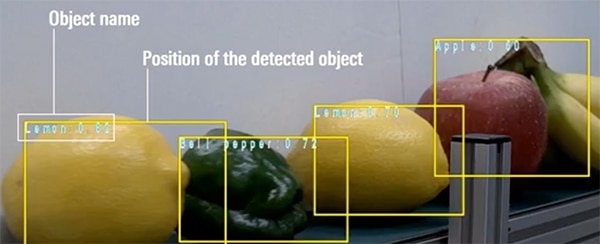

最後に、この例では、検出した物体の周囲にボックスを描き、認識した物体の名称と信頼度を表示しています(図8)。

図8:コンベアベルト上の果物や野菜を検出するアプリケーションにおけるRZ/V2Lの出力例。(画像提供:Renesas Electronics Corporation)

図8:コンベアベルト上の果物や野菜を検出するアプリケーションにおけるRZ/V2Lの出力例。(画像提供:Renesas Electronics Corporation)

RZ/V2Lを使い始めるためのヒントとコツ

Renesas RZ/V2L MPUで機械学習を始めようとする開発者は、立ち上げに活用できるリソースが多くあることに気づくでしょう。以下では、開発者が留意すべき、開発を簡素化してスピードアップするための「ヒントとコツ」をいくつかご紹介します。

- 開発ボードと既存のサンプルで始めて、アプリケーションの展開と実行の感触をつかみます。

- 複数の推論を実行する必要がある場合は、実行可能なモデルを外部メモリに保存し、DRP-AI機能を使用してモデルを素早く切り替えられるようにします。

- RenesasのRZ/V組み込みAI MPUのサイトにあるドキュメントやビデオを確認します。

- DRP-AIトランスレータをダウンロードします。

- RZ/V2L DRP-AIのサポートパッケージをダウンロードします。

これらの「ヒントとコツ」に従えば、始める際に大幅に時間を節約でき、悩み事も減るでしょう。

まとめ

MLとAIは多くのエッジアプリケーションに導入されており、リアルタイムで物体を認識する機能がますます重要になっています。設計者にとって、エッジでAI/MLを実行するために最適なアーキテクチャを見つけることは困難です。GPUは消費電力が大きい傾向があり、MCUは演算能力が十分でない場合があります。

上述したように、DRP-AIを搭載したRenesas RZ/V MPUシリーズは、ハードウェアでAIを高速化するなどの利点があり、充実したツールチェーンや試作サポートも備えています。

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、DigiKeyの意見、信念および視点またはDigiKeyの公式な方針を必ずしも反映するものではありません。