Design GatewayのIPコアを使ってXilinx VCK190評価キット上でAIアプリケーションを高速化

2022-11-18

XilinxのVersal AIコアシリーズ デバイスは、AI推論という最も困難で比類ない問題を解決するために、高い計算効率のASICクラスのAI計算エンジンを柔軟なプログラム可能ファブリックと組み合わせて使うことで、あらゆるワークロードに対して効率を最大化できるだけでなく低消費電力と低遅延を実現できるアクセラレータを備えたAIアプリケーションを構築できるように設計されています。

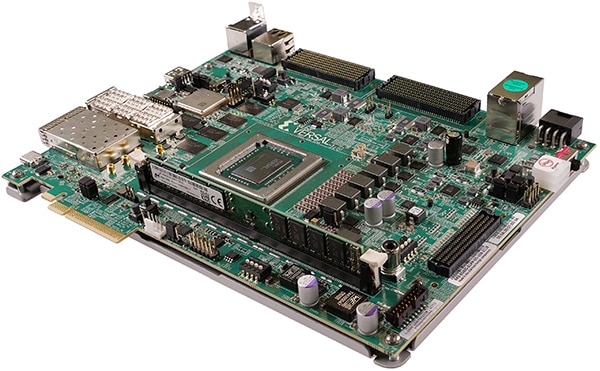

Versal AIコアシリーズVCK190評価キットは、本シリーズの製品ラインアップの中で最も優れたAI性能を持つVC1902デバイスを搭載しています。このキットは、高スループットのAI推論や信号処理の計算性能を必要とする設計向けに作られています。VCK190キットは、現行のサーバークラスCPUの100倍の演算能力を持ち、様々な接続オプションを備えているため、クラウドからエッジまでの多様なアプリケーションの評価およびプロトタイピングに理想的なプラットフォームを提供します。

図1:Xilinx Versal AIコアシリーズ VCK190評価キット(画像提供:AMD, Inc.)

図1:Xilinx Versal AIコアシリーズ VCK190評価キット(画像提供:AMD, Inc.)

VCK190評価キットの主な特長

- オンボードVersal AIコアシリーズ デバイス

- Versal ACAP XCVC1902量産用シリコンを搭載

- AIおよびDSPエンジンにより、現行のサーバークラスCPUの100倍の計算性能を実現

- パートナーがあらかじめ用意したリファレンス設計により、迅速なプロトタイピングが可能

- 最新のコネクティビティ技術で、最先端のアプリケーション開発を実現

- NVMe SSDやホストプロセッサなどの高性能デバイスインターフェース用PCIe® Gen4ハードIPを搭載

- 100G EMACハードIP搭載により、高速100Gネットワークインターフェースを実現

- DDR4およびLPDDR4メモリインターフェースを搭載

- ツールとデバッグ方法を同時に最適化

- AI推論アプリケーション開発用のAIエンジンツール、Vivado® ML、Vitis™統合ソフトウェアプラットフォーム、Vitis AIを搭載

XilinxのVersal AIコアシリーズ デバイスにより、AIインターフェースを高速化

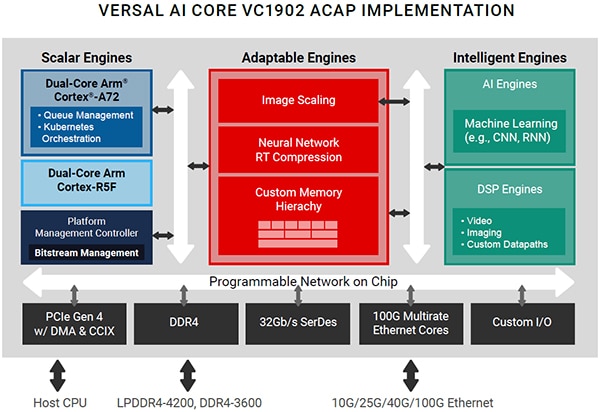

図2:Xilinx Versal AIコアVC1902 ACAPデバイスのブロック図(画像提供:AMD, Inc.)

図2:Xilinx Versal AIコアVC1902 ACAPデバイスのブロック図(画像提供:AMD, Inc.)

Versal® AIコアACAP(Adaptive Compute Acceleration Platform:適応型演算アクセラレーションプラットフォーム)デバイスは、高集積度のマルチコア異種デバイスであり、幅広いAIワークロードに対してハードウェアおよびソフトウェアレベルで動的に適応できるため、AIエッジコンピューティングアプリケーションまたはクラウドアクセラレータカードに最適です。このプラットフォームには、組み込みコンピューティング用の次世代スカラーエンジン、ハードウェアの柔軟性を高める適応型エンジン、およびインテリジェントエンジン(推論用の革新的なAIエンジンと信号処理用のDSPエンジンで構成)が統合されています。これにより、AI/MLワークロードに対する従来のFPGAおよびGPUの性能、遅延、および電力効率を超える適応型のアクセラレータが誕生しました。

Versal ACAPプラットフォームのハイライト

- 適応型エンジン:

- カスタムメモリ階層により、アクセラレータカーネルのデータの移動と管理を最適化

- ニューラルネットワークのリアルタイムでの圧縮と画像スケーリングなどの前処理/後処理機能

- AIエンジン(深層学習処理ユニット:DPU)

- XCVC1902デバイスで最大133 INT8 TOPSの性能を持つ、ベクトルプロセッサのタイル型アレイ。このアレイをディープラーニング処理ユニット(DPU)と呼びます。

- CNN、RNN、MLPなどのニューラルネットワークに最適。進化的アルゴリズム向けに最適化できる進化型ハードウェア

- スカラーエンジン

- クアッドコアARMプロセッシングサブシステム。セキュリティ・電力・ビットストリーム管理のためのプラットフォーム管理コントローラ

VCK190のAI推論性能

VCK190は、最新のサーバークラスのCPUと比べて100倍以上の計算性能を実現しています。以下は、6基のC32B6 DPUコアによるAIエンジン実装の性能例です。次の表は、VCK190でDPUを1250MHzで動作させた場合のさまざまなニューラルネットワークサンプルのスループット性能(フレーム/秒:fps)を示しています。

|

表1:VCK190のAI推論性能の例

VCK190のAI性能の詳細については、『Vitis AI Library User Guide (UG1354), r2.5.0』(https://docs.xilinx.com/r/en-US/ug1354-xilinx-ai-sdk/VCK190-Evaluation-Board)をご覧ください。

Design GatewayのIPコアは、どのようにしてAIアプリケーションの性能を高速化するのでしょうか?

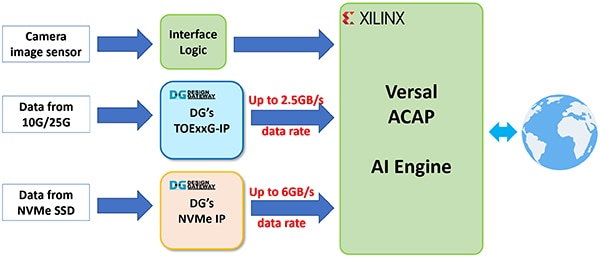

Design GatewayのIPコアは、CPUを介さずにネットワーク接続およびデータ保存のプロトコルを処理するように設計されています。これにより、CPUシステムは、複雑なプロトコル処理の負荷を完全にオフロードできるため、AI推論、データの前処理・後処理、ユーザーインターフェース、ネットワーク通信、データストレージへのアクセスなどのAIアプリケーションにその計算能力を最大限に活用できるので、最高の性能を実現することが可能になります。

図3(ブロック図):Design GatewayのIPコアを用いたAIアプリケーションの例(画像提供:Design Gateway)

図3(ブロック図):Design GatewayのIPコアを用いたAIアプリケーションの例(画像提供:Design Gateway)

Design GatewayのTCPオフロードエンジンIP(TOExxG-IP)の性能

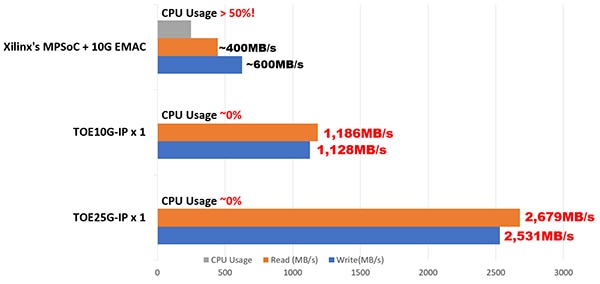

従来のCPUシステムでは、10GbEや25GbEを超える高速・高スループットのTCPデータストリームを処理するために、CPU時間の50%以上を必要とするので、AIアプリケーションの全体的な性能が低下します。XilinxのMPSoC Linuxシステムでの10G TCP性能テストによると、10GbE TCP伝送時のCPU使用率は50%以上であり、TCP送受信データ伝送速度は10GbE速度のおよそ40%~60%(つまり、400MB/s~600MB/s)だったとのことです。

Design GatewayのTOExxG-IPコアを導入することで、10GbEおよび25GbEを介したTCP伝送におけるCPU使用率をほぼ0%に抑え、Ethernet帯域の使用率を100%に近づけることができます。これにより、完全ハードウェアロジックで直接、TCPネットワークを介してデータを送受信し、最小限のCPU使用率と最小限の遅延でVersal AIエンジンにデータを供給することができます。以下の図4は、TOExxG-IPシステムとMPSoC Linuxシステムの間で、CPU使用率とTCP伝送速度を比較したものです。

図4:MPSoC LinuxシステムとDesign GatewayのTOExxG-IPコアによる、10G/25G TCP伝送性能の比較(画像提供:Design Gateway)

図4:MPSoC LinuxシステムとDesign GatewayのTOExxG-IPコアによる、10G/25G TCP伝送性能の比較(画像提供:Design Gateway)

Versalデバイス用のDesign Gateway製TOExxG-IP

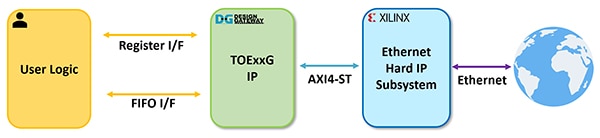

図5:TOExxG-IPシステムの概要(画像提供:Design Gateway)

図5:TOExxG-IPシステムの概要(画像提供:Design Gateway)

TOExxG-IPコアは、TCP/IPスタックを(固定配線ロジックで)実装し、Xilinx製EMACのハードIPおよびEthernetサブシステムモジュールと接続することで、10G/25G/100G Ethernet速度との下位層ハードウェアインターフェースを提供します。TOExxG-IPのユーザーインターフェースは、制御信号用のレジスタインターフェースと、データ信号用のFIFOインターフェースで構成されています。TOExxG-IPは、AXI4-STインターフェースを介してXilinxのEthernetサブシステムに接続するように設計されています。TOExxG-IPのユーザーインターフェースのクロック周波数は、XilinxのEthernetインターフェースの速度(例:156.625MHz、322.266MHz)によって決まります。

TOExxG-IPの特長

- CPUを使用せずにフルTCP/IPスタックを実装

- 1台のTOExxG-IPで1セッションをサポート

- 複数のTOExxG-IPインスタンスを使うことにより、マルチセッションを実現可能

- サーバーモードとクライアントモードの両方に対応(パッシブ/アクティブ、オープンおよびクローズ)

- ジャンボフレームに対応

- 標準的なFIFOインターフェースによるシンプルなデータインタフェース

- シングルポートRAMインターフェースによるシンプルな操作性

下の表2は、XCVC1902-VSVA2197-2MP-ES FPGAデバイス上のFPGAリソースの使用量を示しています。

|

表2:Versalデバイスの実行統計の例

TOExxG-IPの詳細はデータシートに記載されており、以下のリンクにあるDesign Gatewayウェブサイトからダウンロードすることができます。

Design GatewayのNVMe Host Controller IPの性能

PCIe Gen3 x4またはPCIe Gen4 x4によるNVMeストレージインターフェースの速度は、最大32Gbpsおよび64Gbpsのデータ伝送速度を備えています。これは、10GbE Ethernetの3~6倍の速度です。複雑なNVMeストレージプロトコルをCPUで処理する場合に、できるだけ高速なディスクアクセスを実現するには、10GbEを介するTCPプロトコルよりも多くのCPU時間が必要になります。

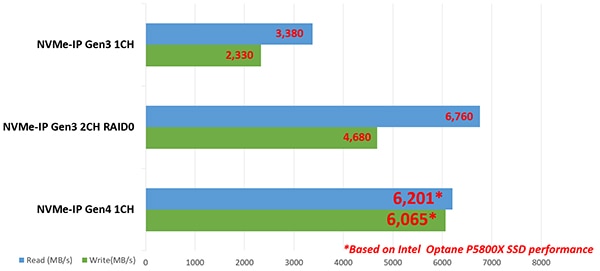

この問題を解決するため、Design Gatewayでは、CPUを使用せずにNVMe SSDと直接通信できるスタンドアロンのNVMeホストコントローラとして稼働可能なNVMe IPコアを開発しました。これにより、NVMe PCIe Gen3 & Gen4 SSDに高い効率と性能でアクセスできるようになるので、NVMeプロトコルの知識がなくても、ユーザーインターフェースと標準機能が簡素化され、使いやすくなります。NVMe PCIe Gen4SSDの性能・伝送速度は、図6に示すように、NVMe IPにより最大6GB/sにまで達します。

図6:NVMe PCIe Gen3 & Gen4 SSDとDesign GatewayのNVMe-IPコアの性能比較(画像提供:Design Gateway)

図6:NVMe PCIe Gen3 & Gen4 SSDとDesign GatewayのNVMe-IPコアの性能比較(画像提供:Design Gateway)

Versalデバイス用のDesign Gateway製NVMe-IP

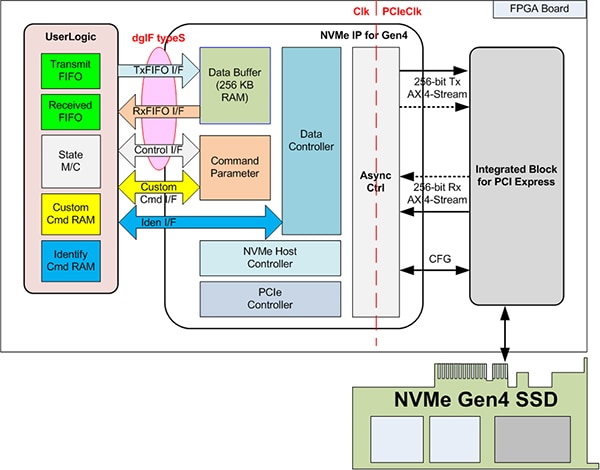

図7:NVMe-IPシステムの概要(画像提供:Design Gateway)

図7:NVMe-IPシステムの概要(画像提供:Design Gateway)

NVMe-IPの特長

- アプリケーションレイヤ、トランザクションレイヤ、データリンクレイヤ、および物理レイヤの一部を実装でき、CPUまたは外部DDRメモリを使用せずにMVMe SSDにアクセス可能

- Xilinx PCIe Gen3 & Gen4ハードIPで動作可能

- 外部メモリインターフェースを必要とせず、BRAMやURAMをデータバッファとして利用可能

- 6つのコマンド(Identify、Shutdown、Write、Read、SMART、Flush)をサポート(オプションで追加コマンドのサポートを利用可能)

XCVC1902-VSVA2197-2MP-E-S FPGAデバイスのFPGAリソース使用量を表2に示します。

|

表3:Versalデバイスの実装統計の例

NVMe-IPの詳細はデータシートに記載されており、以下のリンクにあるDesign Gatewayウェブサイトからダウンロードすることができます。

Gen4向けNVMe IPコアに関するXilinxのデータシート

まとめ

TOExxG IPコアとNVMe IPコアはどちらも、リアルタイムAIアプリケーションに不可欠なTCPやNVMeストレージプロトコルなど、計算とメモリを大量に使用するプロトコルから、CPUシステムを完全に解放することにより、AIアプリケーションの性能を高速化することに貢献します。これにより、XilinxのVersal AIコアシリーズ デバイスは、ネットワークやデータストレージのプロトコル処理による遅延やボトルネックやなしに、AI推論や高性能コンピューティングアプリケーションを実行することができます。

VCK190評価キットとDesign GatewayのネットワークおよびストレージIPソリューションにより、XilinxのVersal AIコアデバイス上で、FPGAリソースの使用量を最小限に抑え、非常に高い電力効率を実現することで、AIアプリケーションの性能を最適化することができます。

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、DigiKeyの意見、信念および視点またはDigiKeyの公式な方針を必ずしも反映するものではありません。